IntroducciónAquí plantéxase implementar o módulo descrito no diagrama de bloques encargado de que un dato de 12 bits apareza á saida dun dos convertidores DAC121S101 presentes no módulo PMOD DA2 de Digilent.

Cada un destes conversores consiste nunha entrada serie e unha saida analóxica, ademáis de outros sinais de sincronización. A tarefa do módulo a implementar consistirá, por tanto, en capturar un dato en paralelo nun rexistro de desprazamento, engadir uns bits de control e transmitilo cara ó convertidor vía serie.

O controlador que figura implementado na páxina do departamento, ao que anteriormente se fixo mención, está diseñado para o módulo PMOD DA1, que incorpora 2 convertidores de 2 canles, e adaptalo para a aplicación actual conlevaría un grande desperdicio de área na FPGA debido a que somentes precisamos unha canle. Por outra banda, unha das características do módulo PMOD DA2 de Digilent, é que conecta as entradas de sincronización de ámbolos dous convertidores ao mesmo punto, polo que cando se transmite un dato a un convertidor é necesario transmitilo ao outro, e por tanto non se pode ignorar a presencia deste segundo convertidor. Estas dúas razóns leváronnos a reescribir desde cero o controlador para o convertidor, de maneira que somentes se empregan os recursos imprescindibles.

ImplementaciónA transmisión dos datos vía serie a un convertidor DAC121S101 realízase mediante un protocolo moi sinxelo. Por un lado transmítese un sinal de reloxo que lle indica os instantes de mostreo da entrada serie, e por outra línea recibe un sinal de inicio de trama. A trama consistirá en dous bits indiferentes, dous de modo de operación e 12 para o valor de voltaxe a xerar. A ecuación que relaciona a entrada dixital coa saida analóxica é moi sinxela:

(valor dixital)*(tensión de referencia)/4096

O convertidor mostrea a trama nos flancos de baixada do sinal de reloxo que se lle comunica, polo que a introducción desta na línea serie sincronizarémola por flancos de subida.

O diseño modular interno parece por tanto evidente: un rexistro paralelo/serie, un contador e unha máquina de estados. Sen embargo esto complícase debido a que a máxima frecuencia que admite o convertidor no sinal de reloxo son 30 MHz e o oscilador da placa é de 50 MHz. Ao noso xuicio existen varias solucións a este problema:

a) o controlador pode actuar na súa totalidade a unha frecuencia inferior á do resto do sistema. Poderíase, por exemplo, dividir o sinal do oscilador entre 10, e transmitir un bit da trama en cada periodo de reloxo. Sen embargo esto faría necesario un circuito a maiores para comunicar este controlador co resto do sistema, que opera a unha frecuencia maior.

b) dividir a frecuencia de reloxo de todo o sistema. Non optaremos esta solución debido a que este sistema podería pasar a formar parte de outro máis complexo e por tanto é interesante optimizar a velocidade.

c) poderíase incorporar un divisor de frecuencia de maneira que a máquina de estados espera ao seguinte período de bit. Sen embargo esto complicaría o diseño da máquina de estados xa que tería que controlar dous contadores.

d)unha solución intermedia pasa por incorporar retardos na máquina de estados, con estados que simplemente esperan. Esta será a solución que adoptaremos, dividindo a frecuencia do oscilador de 50 MHz entre 2, para obter 25MHz, que xa entran dentro da marxe especificada de 30 MHz.

Ficheiro fonte e diagramadac_top.vhdDIAGRAMA.JPG(se non funciona o segundo enlace presionar ENTER sobre a barra de direccións)

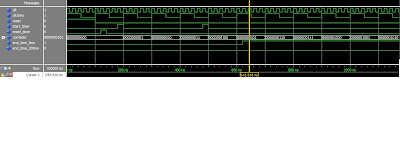

Simulación temporal

Extracto do informe de síntese

Device utilization summary:

---------------------------

Selected Device : 3s200ft256-5

Number of Slices: 17 out of 1920 0%

Number of Slice Flip Flops: 30 out of 3840 0%

Number of 4 input LUTs: 26 out of 3840 0%

Number of IOs: 19

Number of bonded IOBs: 19 out of 173 10%

Number of GCLKs: 1 out of 8 12%

Timing Summary:

---------------

Minimum period: 3.764ns (Maximum Frequency: 265.661MHz)

Minimum input arrival time before clock: 2.444ns

Maximum output required time after clock: 6.216ns

Maximum combinational path delay: No path found

Verificación

Para probar o módulo compreto na placa creamos un sistema moi sinxelo que captura dos interruptores os 8 bits máis significativos do dato a convertir. Os demais supóñense nulos. Instánciase un detector de flancos que xera un sinal cada vez que se acciona un dos pulsadores da placa. Neste momento visualízase este mesmo dato nos led para comprobar que non existen erros nos interruptores e dáse orde ao módulo en proba de iniciar a conversión.

A placa conéctase ao convertidor a través da placa MIB de Digilent. Para elaborar o ficheiro .ucf foi necesario seguir a pista de cada un dos sinais.

O ficheiro resultante consta das seguintes liñas:

# DIGILENT S3 BOARD COMPONENTS

NET "clk" LOC = "T9" ;

#Main clock 50 MHz

# S3 BOARD SWITCHES

# FROM SWITCH 7 (MOST SIGNIFICANT) TO SWITCH 0 (LEAST SIGNIFICANT)

NET "dato<7>" LOC = "K13" ;

NET "dato<6>" LOC = "K14" ;

NET "dato<5>" LOC = "J13" ;

NET "dato<4>" LOC = "J14" ;

NET "dato<3>" LOC = "H13" ;

NET "dato<2>" LOC = "H14" ;

NET "dato<1>" LOC = "G12" ;

NET "dato<0>" LOC = "F12" ;

# S3 BOARD PUSHBUTTONS

# FROM BTN3 TO BTN 0

NET "convertir" LOC = "M14" ;

NET "reset" LOC = "M13" ;

# S3 BOARD LEDs

# FROM LED 7 (MOST SIGNIFICANT) TO LED 0 (LEAST SIGNIFICANT)

NET "dato_led<7>" LOC = "P11" ;

NET "dato_led<6>" LOC = "P12" ;

NET "dato_led<5>" LOC = "N12" ;

NET "dato_led<4>" LOC = "P13" ;

NET "dato_led<3>" LOC = "N14" ;

NET "dato_led<2>" LOC = "L12" ;

NET "dato_led<1>" LOC = "P14" ;

NET "dato_led<0>" LOC = "K12" ;

# S3 BOARD 4-DIGIT 7-SEGMENT DYNAMIC DISPLAY ANODES

# FROM ANODE 3 (MOST SIGNIFICANT DIGIT) TO ANODE 0 (LEAST SIGNIFICANT DIGIT)

# ACTIVE LOW ANODES

NET "sclk" LOC = "C11" ;

NET "sdin2" LOC = "T3" ;

NET "sdin1" LOC = "E10" ;

NET "sync" LOC = "C10" ;

Con esto damos por concluido o diseño do controlador do convertidor DA, anque é posible realizar unha pequena optimización introducindo un rexistro de desprazamento para conmutar o segundo conversor a modo de baixo consumo. De facerse farase ao final do proxecto.

A primeira instancia que se ve é o divisor de frecuencia usado para xerar o sinal de 1 kHz a partires do reloxo do sistema de 50 MHz e a outra instancia é a interfaz do teclado propiamente dita, con tódolos rexistros, máquina de estados, temporizador, ... necesarios para o funcionamento.

A primeira instancia que se ve é o divisor de frecuencia usado para xerar o sinal de 1 kHz a partires do reloxo do sistema de 50 MHz e a outra instancia é a interfaz do teclado propiamente dita, con tódolos rexistros, máquina de estados, temporizador, ... necesarios para o funcionamento. 2) FUNCIONAMENTO:

2) FUNCIONAMENTO: